Basic Elements(基本组成元素)

Processor(处理器)

Main Memory(内存)

称为实际内存(实存 real memory)或主存(primary memory)

I/O modules(输入输出模块)

次级存储设备(磁盘)

通信设备

终端

System bus(系统总线)

处理器、内存和 I/O 模块间的通信

Prcessor Registers(CPU 寄存器)

存在于CPU的内存,启用CPU以最小化主存引用。CPU寄存器保持位置或内存的小数据,并且是处理器的一个组成部分。

是一种非常快速的计算机存储器,主要用于非常快速地执行程序和其他主要操作。

处理器层次:CPU <= => 寄存器 <= => 缓存 <= => 内存

CPU 寄存器的操作

当我们提供输入时,这些被存储并存储在寄存器进程中,并且输出仅来自寄存器。

因此,基本上寄存器将执行以下操作。

- 获取:获取用户的指令以及以排序方式存在于主内存中的指令

- 解码:第二个操作是对需要执行的指令进行解码。因此,CPU 将知道指令是什么

- 执行:一旦指令被解码,CPU 就会执行执行操作。完成后,结果将显示在用户屏幕上

下面是两类 CPU 寄存器

1. User-Visible Registers(用户可见寄存器)

可以被机器语言访问存取,可用于所有程序(应用程序/系统程序)

2. Control and Status Registers(控制和状态寄存器)

大多数用户不可见,用于控制处理器的操作

PC计数器 Program Counter:包含下一条指令的地址

寄存器将保存需要获取和执行或执行的下一条指令的地址。当指令被获取时,该值将递增,因此将始终保存要运行的下一条指令的地址。

IR指令寄存器 Instruction Registers:包含最近获取的指令

一旦从主存储器中获取指令,它就会存储在指令寄存器 IR 中。控制单元从这里获取指令对其进行解码,并通过向所需组件发送所需信号来执行它。

Program Status Word (PSW) :运行状态字

Interrupt enable/disable(中断启用/禁用)

……

所有的处理器设计还包括一个或一组寄存器,通常称为程序状态字(Program Status Word,PSW ),它包含状态信息。PSW 通常包含条件码和其他状态信息,如中断允许/禁止位和内核/用户态位。 条件码( condition code,也称为标记)是处理器硬件为操作结果设置的位。例如,算术运算可能产生正数、负数、零或溢出的结果,除了结果自身存储在一个寄存器或存储器中之外,在算术指令执行之后,也随之设置一个条件码。这个条件码之后可作为条件分支运算的一部分被测试。条件码位被收集到一个或多个寄存器中,通常它们构成了控制寄存器的一部分。机器指令通常允许通过隐式访问来读取这些位,但不能通过显式访问进行修改,这是因为它们是为指令执行结果的反馈而设计的。

Instruction Execution(指令执行)

取址 => 译码 => 执行 => 取址 => 译码 => 执行 => ……

CPU 的程序计数器(PC)保存下一个要获取的指令的地址 获取的指令放置在指令寄存器(IR)中 每次取出后 CPU 的程序计数器 (PC) 递增

执行过程

CPU 的程序计数器(PC)保存接下来要获取的指令的地址,取出的指令放在指令寄存器(IR)中,每次取出后程序计数器(PC)都会增加

指令周期

执行单个指令需要的执行过程——取出并执行,不同指令的指令周期不同,由若干机器周期来表示

指令的执行阶段

单指令周期

Interrupts(中断)

其他模块(I/O,时钟等)可能会中断处理器任务的正常排序,从而使 CPU 具有异步处理的能力。I/O 设备可以停止 CPU 运行以提供一些必要的服务

为什么需要中断

大多数的 I/O 设备都比处理器慢,中断可以提高 CPU 使用率(improve CPU’s utilization),使处理器不必暂停等待设备

如后文提到的 DMA 中介管理 IO设备

避免 CPU 被程序独占

中断与指令周期

中断处理

多次中断

进程并发

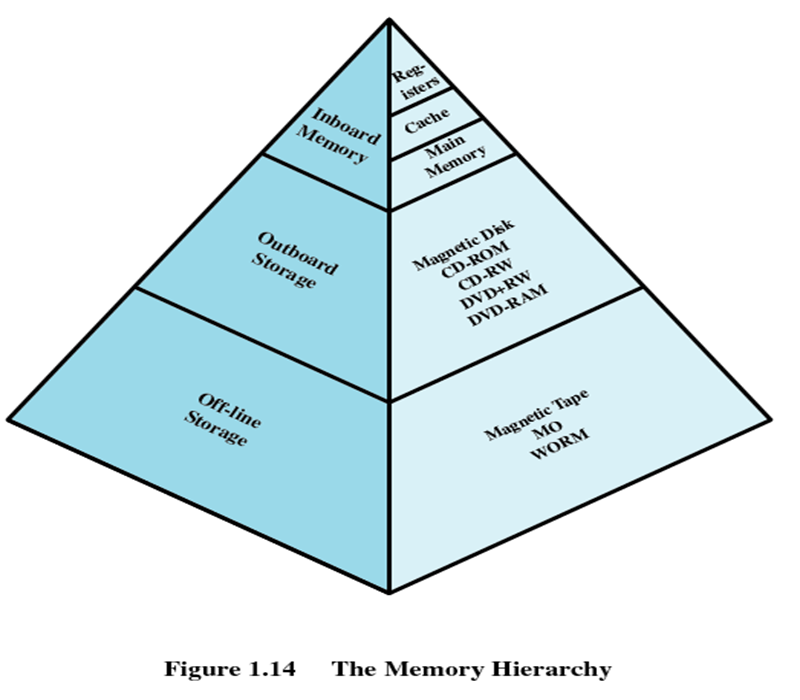

The Memory Hierarchy(内存层次结构)

获得更大的存储容量意味着更慢的访问速度和便宜的价格

更快的访问速度有较小的容量和较高的价格

板上存储器 ==> 板外存储器 ==> 离线存储器(从左向右增加访问时间、提升容量、降低单位成本)

处理器与内存层次:CPU <= => 寄存器 <= => 缓存 <= => 内存 <= => ……

使用内存层次结构有效地组织内存:

Smaller, more expensive, faster memories are supplemented (后备) by larger, cheaper, slower memories

更小、更昂贵、更快的记忆被更大、更便宜、更慢的记忆所补充(后备)

Larger, cheaper, slower memories are cached(缓存) by Smaller, more expensive, faster memories

更大,更便宜,更慢的内存被更小,更昂贵,更快的内存缓存(缓存)

Locality of reference(访问局部性/局部性原理/principle of locality)

局部性原理一定程度上解释了缓存的存在

Spatial locality (空间局部性)

空间

Temporal locality (时间局部性)

时间

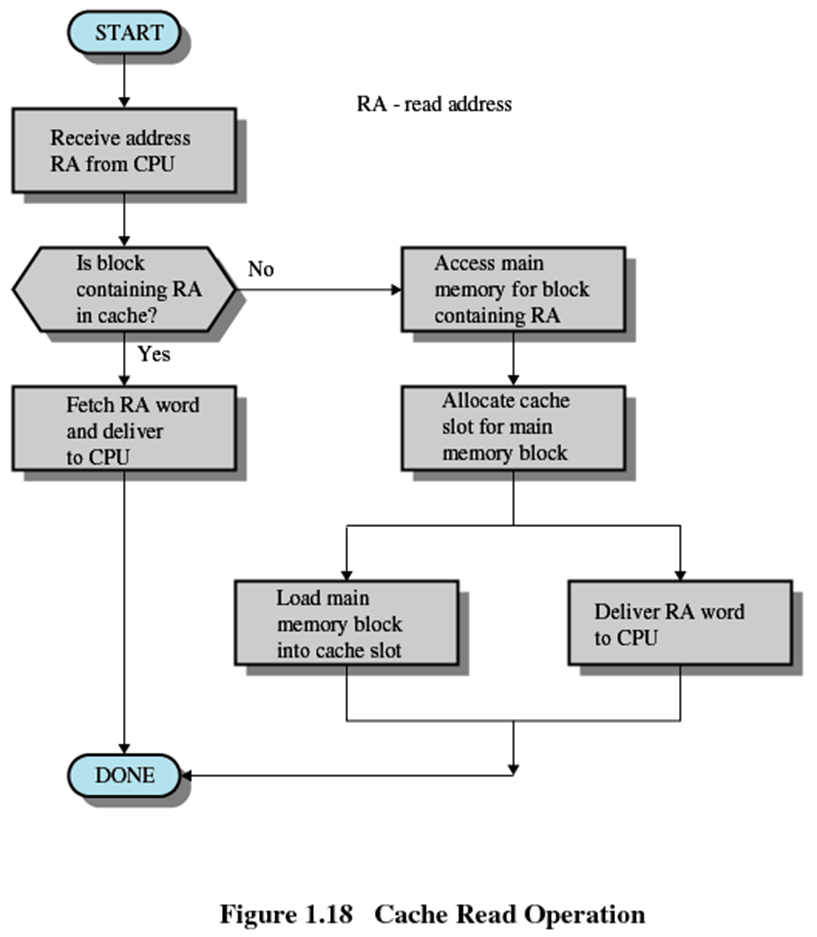

Cache Memory(高速缓存)

缓存: 包含部分主内存的副本

- 处理器首先检查缓存 (Hit)如果找到,只需使用它。并且不需要访问内存(缓存命中)

- 如果在缓存中找不到(Miss),则包含所需信息的内存块将移动到缓存并传递到处理器

缓存命中

如果cpu要读取数据块1,cpu先在高速缓存中查找数据块1,如果找到就直接返回,这就叫“缓存命中”,因为缓存的速度比主存的速度要快很多,缓存命中大大提高了效率。

缓存不命中

如果cpu要读取数据块5,数据块5不在缓存中,那么叫做“缓存不命中”。那么cpu就要去主存中取到数据块5,然后把数据块5放到高速缓存中,如果缓存中的数据存满了,就要覆盖现存的一个数据块。

I/O Communication (I/O通信)

Programmed I/O (可编程 I/O)

CPU向 IO 设备发送指令后进入盲等待,CPU 不断检测直到 I/O 设备操作完成,且亲自运输数据到 Memory

这种方式非常浪费 CPU 资源,有长时间的 CPU 等待

Interrupt-Driven I/O(中断驱动 I/O)

CPU向 IO 设备发送指令后继续处理其他事务,直到 I/O 设备操作完成并发出一个中断到 CPU ,CPU 中断事务并过来处理 IO 数据,且亲自运输数据到 Memory

这种方式比上一种更好,但仍然浪费 CPU 资源去处理不必要的细节(由于 IO 设备与 CPU 速度不一样)

Direct Memory Access / DMA(中介管理 I/O 设备、直接存储器访问)

DMA 作为中介指挥 I/O 设备批量完成任务,管理 I/O status ,处理器授予I/O - Memory 访问权限

CPU 向 DMA 发出指令后授予 DMA 总线控制权,DMA开始处理 IO 任务,此时 CPU 执行其他事务

DMA 管理的 IO 执行结束,向 CPU 发出中断,与其交接总线控制权,此时 IO 事务结束

更大地解放了 CPU 的运行限制,提高 CPU 利用率,使不同速度的硬件装 置相互沟通

决定块写入缓冲位置的是replace策略

进程管理

OS 的五个 management responsibilities:

Process isolation (进程隔离)

Automatic allocation and management (自动分配和管理)

Support of modular programming (模块化程序设计)

Protection and access control (保护与存取控制)

Long-term storage (长期存储)

虚拟内存 / 虚拟机

允许程序员从逻辑角度处理内存问题

在执行连续进程时,一个进程被写出到辅助存储区,后续进程被读入,这两者之间没有中断

页(page)

允许进程由许多固定大小的块组成,称为页面 每个页面都可以位于主内存中的任何位置

分页式系统提供程序中使用的虚拟地址与 main memory 中的实地址之间的动态映射

Virtual Memory Addressing

存储系统由主存储器和辅助存储器组成

Scheduling and Resource Management (调度和资源管理)

- Fairness (公平性)

- Differential responsiveness (差别响应性)

- Efficiency (高效性)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)